FD-SOI FPGA(2025)

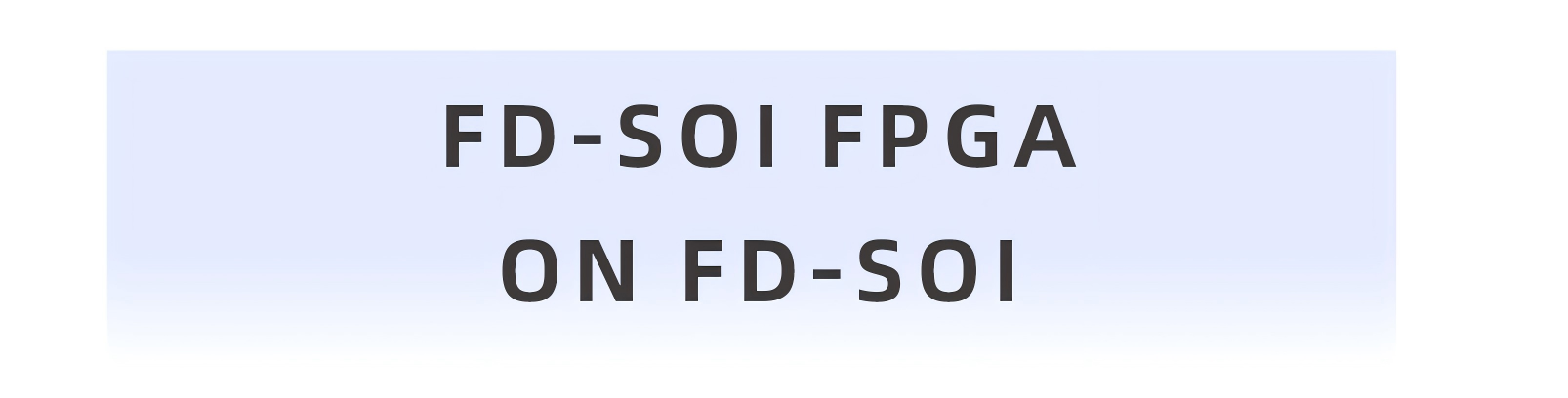

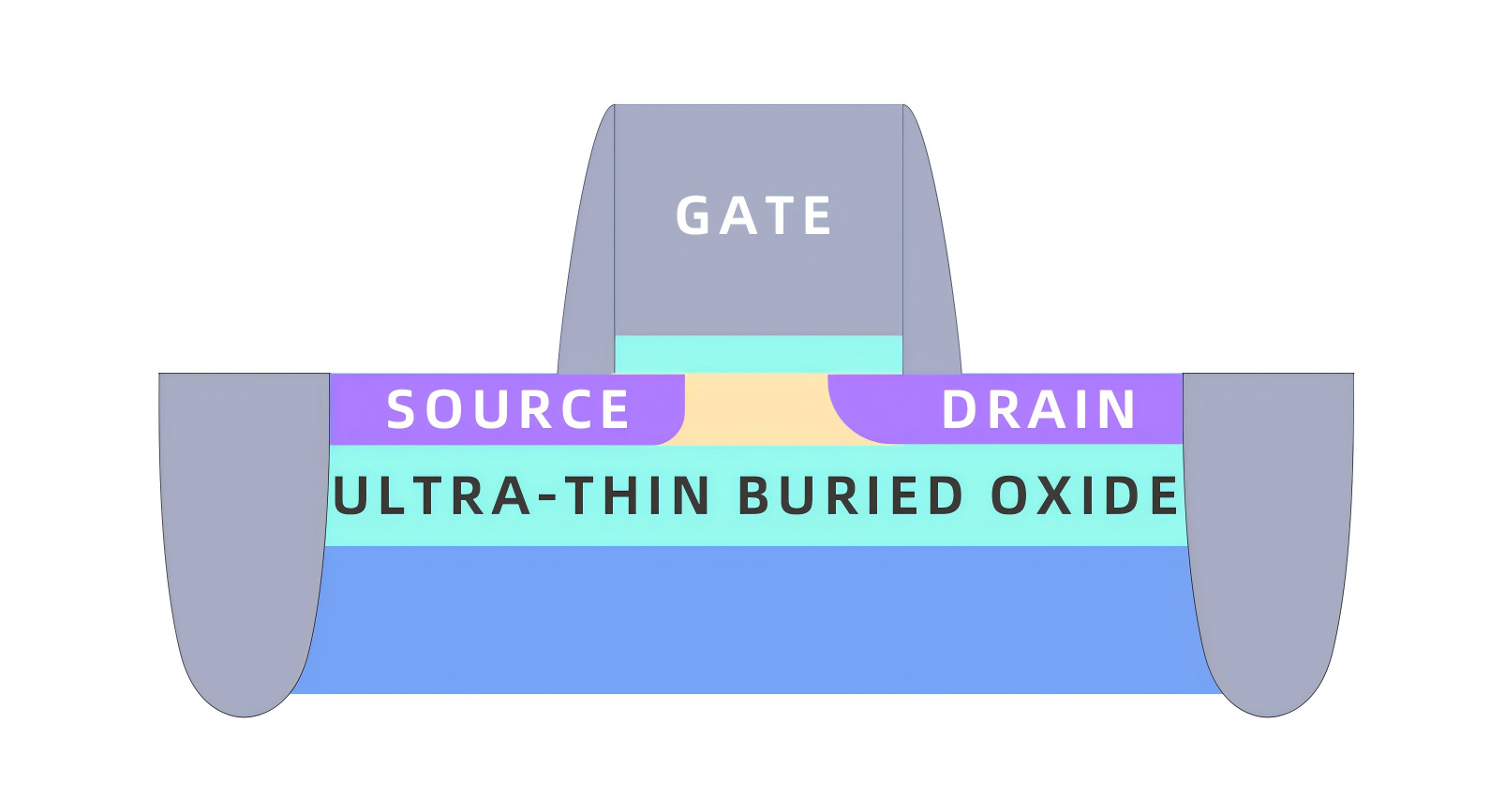

Features of FD-SOI FPGAs

Features of FD-SOI FPGAs

Improvements in circuit hierarchies

Improvements in circuit hierarchies

Better performance, higher frequency, faster speeds

Better performance, higher frequency, faster speeds

Compared with the contemporaneous body collision process, the FD-SOI-based circuit can increase the operating frequency by 30% by increasing the forward body bias FBB.

The device layer is separated from the bottom of the village, and the static power consumption is lower

The device layer is separated from the bottom of the village, and the static power consumption is lower

With reverse body bias RBB, the FD-501 base circuit can operate at lower voltage ratings and reduce quiescent power consumption by 70%. FD-SOI FPGAs are suitable for IoT, artificial intelligence, low-power computing, and 5G applications.

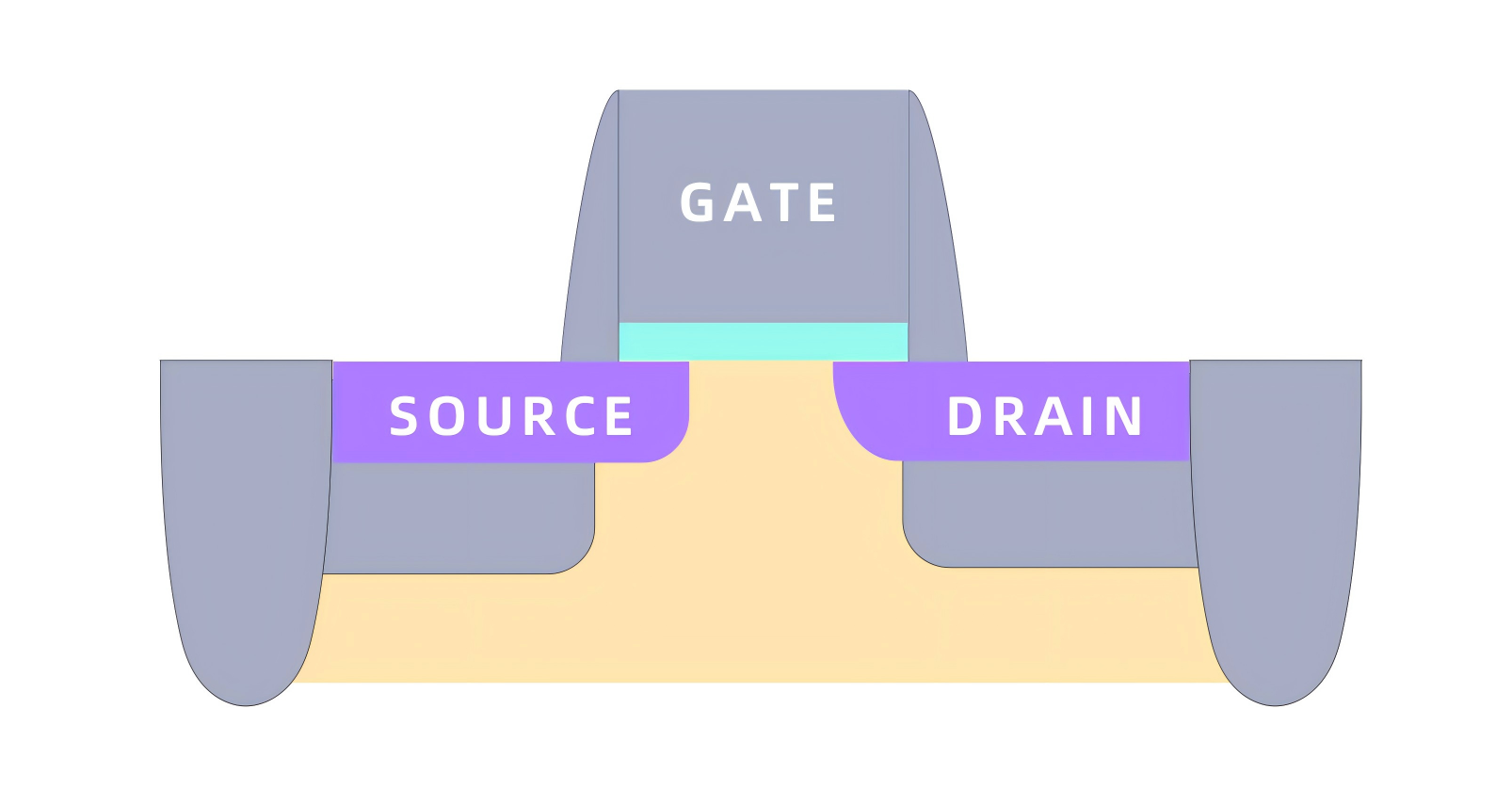

![]() Continuing the plane process, cost-effective

Continuing the plane process, cost-effective

Compared to the FinFET process, the FD-SOI process requires fewer masks, is more cost-effective, and makes it easier to migrate designs from traditional bulk silicon processes.

![]() Low soft error rate and excellent reliability

Low soft error rate and excellent reliability

Compared with traditional bulk silicon and advanced FinFET processes, FD-SOI-based circuits have a lower intrinsic soft error rate, which is more suitable for high-reliability fields such as automotive electronics, aerospace, power equipment, and life support systems. Artificial intelligence, low-power computing, and 5G applications.

Product-level benefits

Product-level benefits

![]() 75% lower power consumption

75% lower power consumption ![]() The SEU is less than 1.0e-8Upset/bit/day

The SEU is less than 1.0e-8Upset/bit/day ![]() Adaptive management of power consumption and performance

Adaptive management of power consumption and performance

![]() Applicable application fields

Applicable application fields

Artificial intelligence, edge computing, automotive electronics, Internet of Things, consumer terminals, electric power, civil aerospace